Microprocessors and Microcontrollers: Unit IV: (d) Serial Data Transfer (USART) 8251

8251A Status Word

Review Questions 1. Describe the status control words in 8251. 2. Draw and explain the mode instruction and command instruction formats in 8251.

8251A Status Word

AU

: Dec.-07

In

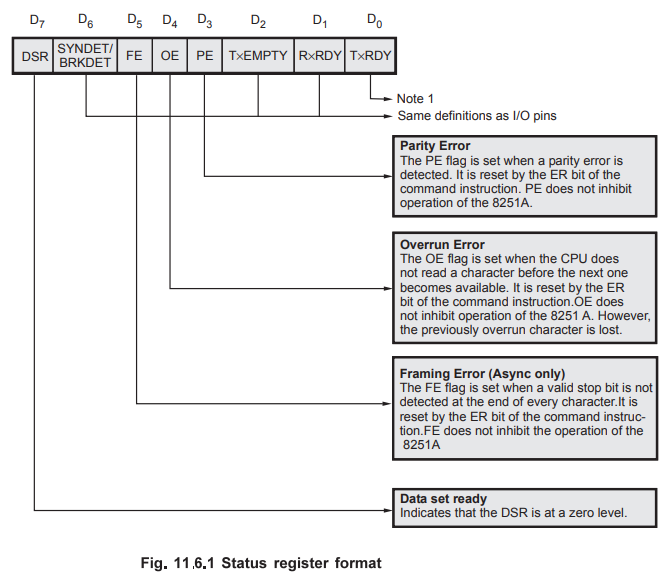

the data communication systems it is often necessary to examine the

"status" of the transmitter and receiver. It is also necessary for

CPU to know if any error has occurred during communication. The 8251A allow the

programmer to read above mentioned information from the status register any

time during the functional operation. Fig. 11.6.1 shows the format of status

register.

Error Definitions

Parity

Error : At the time of transmission of data an even or odd

parity bit is inserted in the data stream. At the receiver end, if parity of

the character does not match with the pre-defined parity, parity error occurs.

Overrun

Error : In the receiver section received character is

stored in the receiver buffer. The CPU is supposed to read this character

before reception of the next character. But if CPU fails in reading the

character loaded in the receiver buffer, the next received character replaces

the previous one and the OVERRUN error occurs.

Framing

Error : If valid stop bit is not detected at the end each

character framing error occurs.

All

these errors, when occur, set the corresponding bits in the status register.

These error bits are reset by setting ER bit in the command instruction.

Review Questions

1. Describe the

status control words in 8251.

AU : Dec.-07, Marks

8

2. Draw and explain the mode instruction and command instruction formats in 8251.

Microprocessors and Microcontrollers: Unit IV: (d) Serial Data Transfer (USART) 8251 : Tag: : - 8251A Status Word