Microprocessors and Microcontrollers: Unit IV: (c) Programmable Interval Timer (PIT/C) 8253/8254

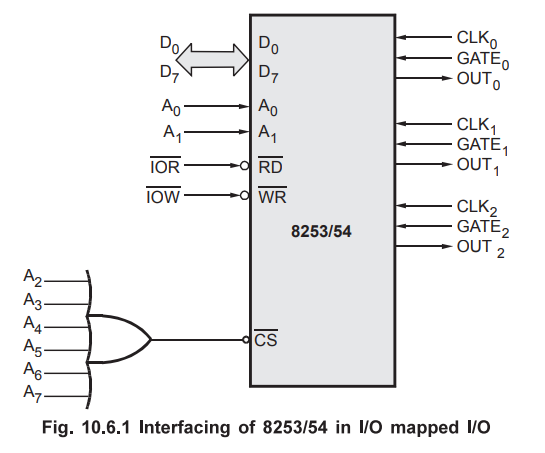

Interfacing of 8253/54 in I/O Mapped I/O

Programmable Interval Timer (PIT/C) 8253/8254

Review Question : 1. Draw and explain the interfacing of 8253 with 8085.

Interfacing of 8253/54 in I/O Mapped I/O

We

know that, 8253/54 has separate address and data lines. Therefore it is

necessary to separate A0-A7 and D0-D7

lines from AD0-AD7 with the help of external decoder and

ALE signal. 8253/54 IC decodes A0 and Al lines internally to select one of its

ports or control register. In I/O mapped I/O, higher byte address bus

duplicates the address of lower address bus, therefore A8 and A9

lines are also indirectly involved in the selection of ports or control

register. The remaining address lines (A7-A2 or A15-A10)

can be used to generate chip select signal. Fig. 10.6.1 shows the interfacing

of 8253/54 with 8085. The 74LS138 IC (3:8 decoder) is used to generate chip

select signal. Another decoder can be used to generate  signals from the

signals from the  signals of 8085.

signals of 8085.

Address

Map :

Review Question

1. Draw and explain the interfacing of 8253 with 8085.

Microprocessors and Microcontrollers: Unit IV: (c) Programmable Interval Timer (PIT/C) 8253/8254 : Tag: : Programmable Interval Timer (PIT/C) 8253/8254 - Interfacing of 8253/54 in I/O Mapped I/O