Electron Devices and Circuits: Unit II: (b) Junction Field Effect Transistor (JEET)

The Pinch-off Voltage Vp (JFET)

Solved Example Problems | Junction Field Effect Transistor

A p-type gate is then diffused into the n-type channel. In this device, a slab of n-type semiconductor is sandwiched between two layers of p-type material, forming two p-n junctions.

The Pinch-off Voltage Vp

•

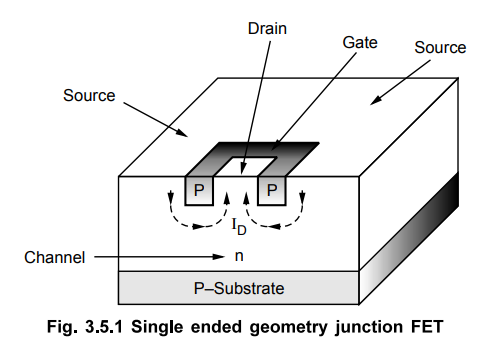

The Fig. 3.5.1 shows a single-ended-geometry junction FET. Here, the substrate

is of p-type material onto which an n-type channel is epitaxially grown. A

p-type gate is then diffused into the n-type channel. In this device, a slab of

n-type semiconductor is sandwiched between two layers of p-type material,

forming two p-n junctions.

•

Let us assume that the p-type region is doped with NA acceptors per cubic

meter, n-type region is doped with ND donors per cubic meter and that the

junction formed is abrupt.

•

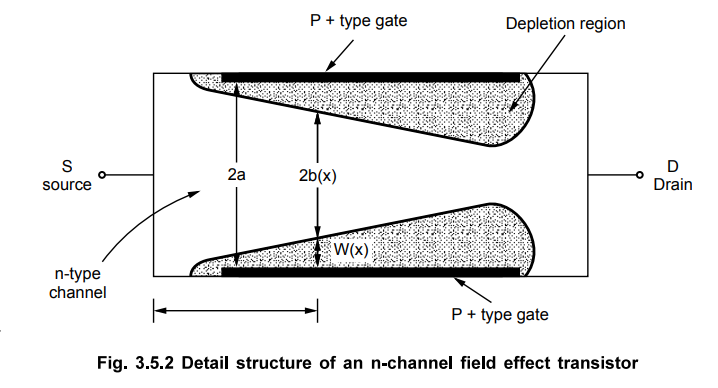

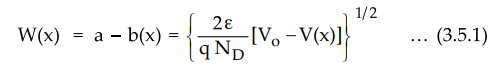

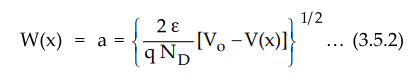

We know that, if NA » ND we have Wp « Wn and for the space-charge width, WR(x)

= W(x) at a distance x along the channel in Fig. 3.5.2.

where

Ɛ

: Dielectric constant of channel material

q

: Magnitude of electric charge

VO

: Junction contact potential at x

V(x)

: Applied potential across space-charge region at x and is a negative number

for an applied reverse bias

a

- b(x) : Penetration W(x) of depletion region into channel at a point x along

channel

•

When the drain current is zero, b(x) and V(x) are independent of x and b(x) =

b. By substituting b(x) = b = 0 we have

•

Now solving for V with assumption |V| << |V| we obtain the pinch-off

voltage Vp (the diode reverse voltage that removes all the free charge from

the channel) as

|VP|

= qND / 2E a2 … (3.5.3)

If

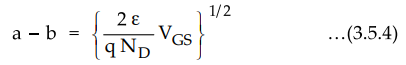

we substitute VGS for VO – V(x) and b(x) = b in equation (3.5.1) we get,

From

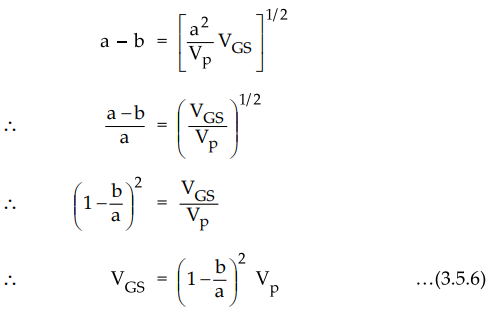

equation (3.5.3) we have

2E

/ qND = a2 / VP … (3.5.5)

Substituting

equation (3.6.5) in equation (3.6.4) we get,

This

equation shows that the voltage VGS (the reverse bias across the

gate junction) is independent of distance along the channel if ID =

0.

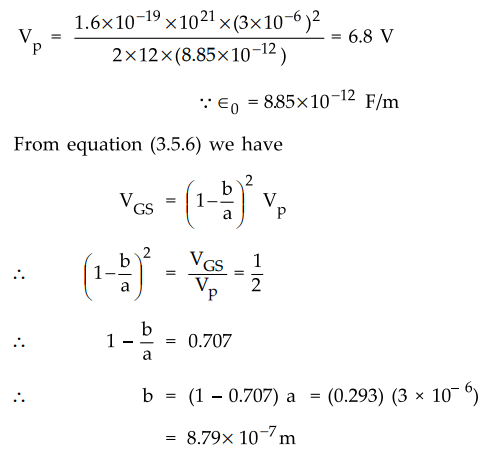

Ex.

3.5.1 For an n-channel silicon FET, find the pinch-off voltage and the channel

half-width.

Assume

: ɑ = 3 × 10-6 m, ND = 1021 electrons/m2,

VGS = ½ Vpv ID = 0 and relative

dielectric constant of silicon = 12.

Sol.

:

Since relative dielectric constant of silicon is 12 we have Ɛ = 12 Ɛ0.

Using values of q and Ɛ0 we have

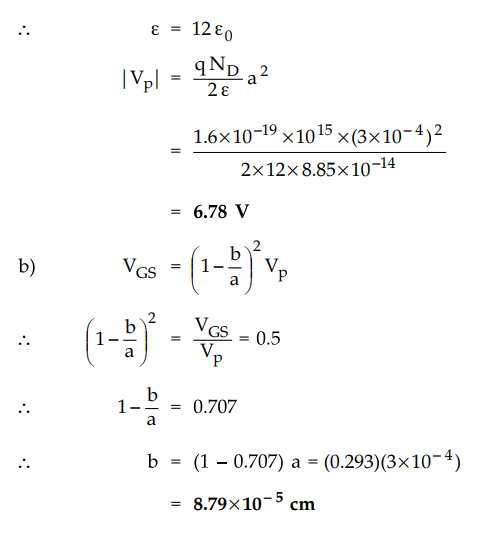

Ex.

3.5.2 For an n-channel silicon FET with a = 3×l0-4 cm and Nd = 1015

electrons/cm-3. Find (a) the pinch off voltage and (b) the channel half-width

for VGS = 0.5 Vp.

AU

: June-16, Marks 6

Sol.

: a) Note that :

Ɛ0

= 8.85 × 10-14 F/cm

q

= 1.6 × 10-19C

Dielectric

constant of silicon = 12

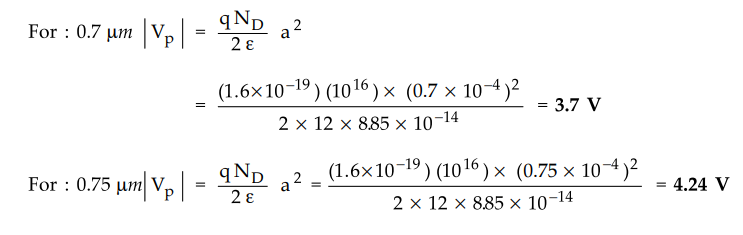

Ex.

3.5.3 Assume that the p+n junction of a uniformly doped silicon n channel JFET

at T = 300 K has doping concentrations of Nɑ = 1018 cm-3

and Nd = 1016 cm-3. Assume that the metallurgical channel

thickness a is 0.7 pm Calculate the pinch off voltage. Also calculate pinch-ojf

voltage if the metallurgical channel thickness a is 0.75 µm

AU

: May-15, Dec.-15, Marks 2

Sol.

:

Here all quantities are in centimeters instead of meters. Channel thickness a=

0.7 ^ti= 0.7 xlO 4 cm. The internal pinch off voltage is given by

Review Question

1. Derive the

expresionfor pinch-off voltage.

AU : Dec.-18

Electron Devices and Circuits: Unit II: (b) Junction Field Effect Transistor (JEET) : Tag: : Solved Example Problems | Junction Field Effect Transistor - The Pinch-off Voltage Vp (JFET)

Related Topics

Related Subjects

Electron Devices and Circuits

EC3301 3rd Semester EEE Dept | 2021 Regulation | 3rd Semester EEE Dept 2021 Regulation