Digital Logic Circuits: Unit III: (c) Shift Registers

Types of Shift Registers

Digital Logic Circuits: Unit III: (c) Shift Registers : Types of Shift Registers

Types of Shift Registers

1. Serial In Serial Out (SISO) Shift Register

Shift

Left Mode

•

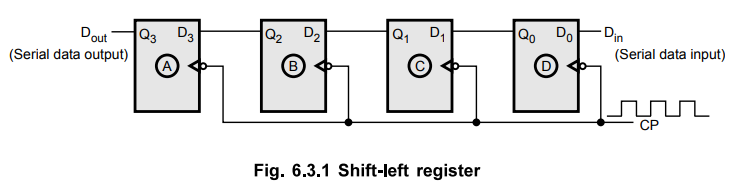

Fig. 6.3.1 shows serial-in serial-out shift-left register.

•

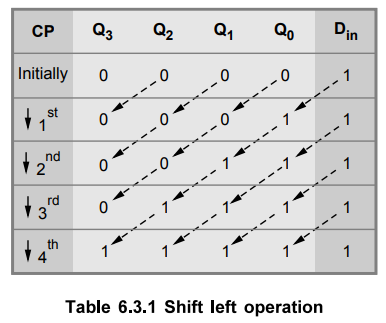

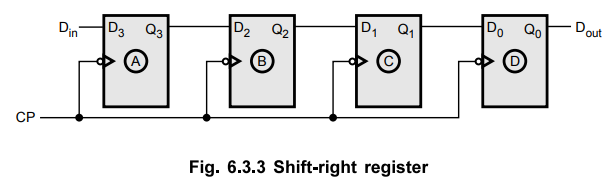

We will illustrate the entry of the four bit binary number 1111 into the

register, beginning with the right-most bit. Initially, register is cleared.

So

Q3 Q2 Q1 = 00 0 0

•

The Table 6.3.1 summarizes the shift left operation.

•

Fig. 6.3.2 shows waveforms for shift left operation.

Shift

Right Mode

•

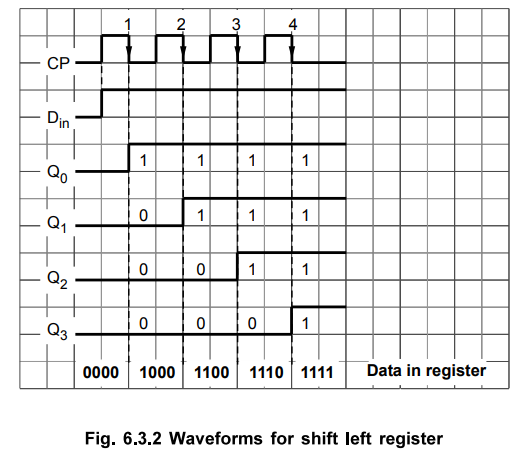

Fig. 6.3.3 shows serial-in serial-out shift-right register.

•

We will illustrate the entry of the four bit binary number 1111 into the register,

beginning with the left-most bit. Initially, register is cleared.

So

Q3 Q2 Q1 = 00 0 0

•

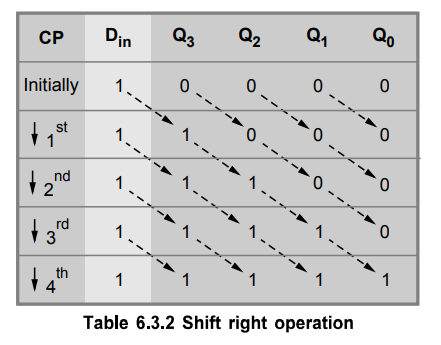

The Table 6.3.2 summarizes the shift right operation.

•

The Fig. 6.3.4 shows waveforms for shift right operation.

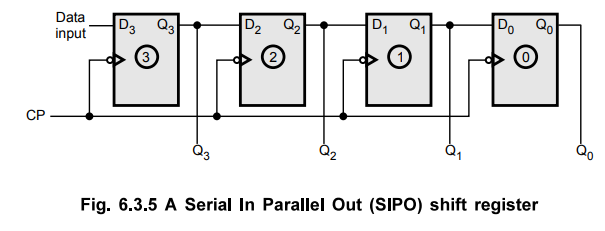

2. Serial In Parallel Out (SIPO) Shift Register

•

The data bits are entered serially into the register but the output is taken in

parallel.

•

Once the data are stored, each bit appears on its respective output line and

all bits are available simultaneously as shown in Fig. 6.3.5.

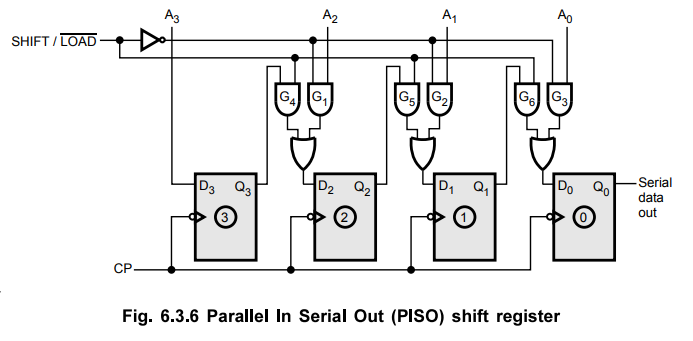

3. Parallel In Serial Out (PISO) Shift Register

•

In this type, the bits are entered in parallel i.e simultaneously into their

respective stages on parallel lines.

•

Fig. 6.3.6 illustrates a four-bit parallel in serial out register.

•

There are four input lines A3, A2, A1, A0

for entering data in parallel into the register.

•  is the control input which allows shift or loading data

operation of the register.

is the control input which allows shift or loading data

operation of the register.

•

When  is low, gates G1, G2, G3 are

enabled, allowing each input data bit to be applied to D input of its

respective flip-flop.

is low, gates G1, G2, G3 are

enabled, allowing each input data bit to be applied to D input of its

respective flip-flop.

•

When a clock pulse is applied, the flip-flops with D = 1 will SET and those

with D = 0 will RESET.

•

All four bits are stored simultaneously.

•

When  is high, gates G1, G2, G3

are disabled and gates G4, G5, G6 are enabled.

This allows the data bits to shift right from one stage to the next.

is high, gates G1, G2, G3

are disabled and gates G4, G5, G6 are enabled.

This allows the data bits to shift right from one stage to the next.

•

The OR gates at the D-inputs of the flip-flops allow either the parallel data

entry operation or shift operation, depending on which AND gates are enabled by

the level on the  input.

input.

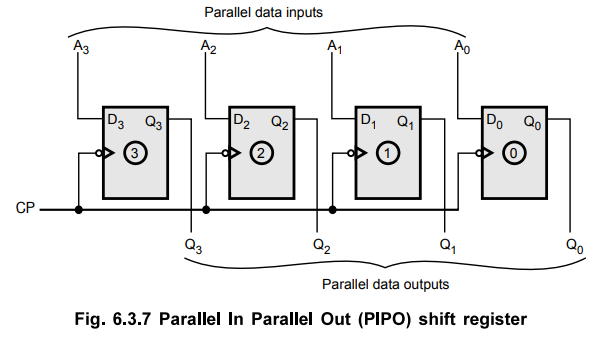

4. Parallel In Parallel Out (PIPO) Shift Register

•

In 'parallel in parallel out register', there is simultaneous entry of all data

bits and the bits appear on parallel outputs simultaneously.

•

Fig. 6.3.7 shows this type of register.

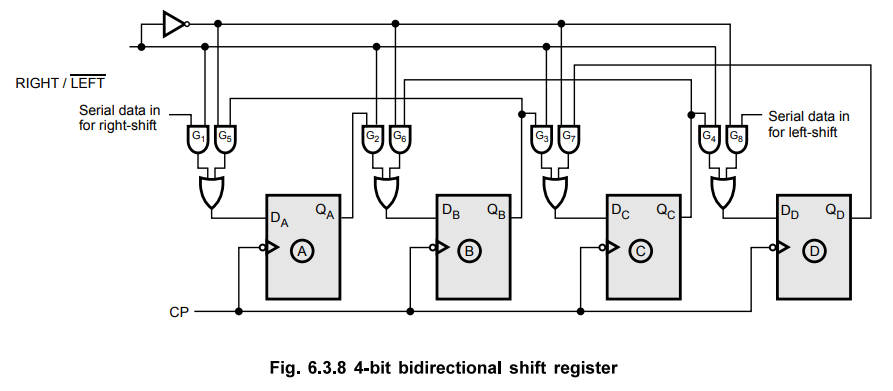

5. Bidirectional Shift Register

•

This type of register allows shifting of data either to the left or to the

right side. It can be implemented by using logic gate circuitry that enables

the transfer of data from one stage to the next stage to the right or to the

left, depending on the level of a control line.

•

Fig. 6.3.8 illustrates a four-bit bidirectional register.

•

The  is the control input

signal which allows data shifting either towards right or towards left.

is the control input

signal which allows data shifting either towards right or towards left.

•

A high on this line enables the shifting of data towards right and a low

enables it towards left.

•

When  signal is high, gates G1, G2, G3,

G4 are enabled.

signal is high, gates G1, G2, G3,

G4 are enabled.

•

The state of the Q output of each flip-flop is passed through the D input of

the following flip-flop.

•

When a clock pulse arrives, the data are shifted one place to the right.

•

When the  signal is low, gates G5, G6, G7,

Gg are enabled.

signal is low, gates G5, G6, G7,

Gg are enabled.

•

The Q output of each flip-flop is passed through the D input of the preceding

flip-flop.

•

When clock pulse arrives, the data are shifted one place to the left.

Bidirectional

Shift Register with Parallel Load

•

When parallel load capability is added to the shift register, the data entered

in parallel can be taken out in serial fashion by shifting the data stored in

the register. Such a register is called bidirectional shift register with

parallel load.

•

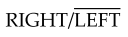

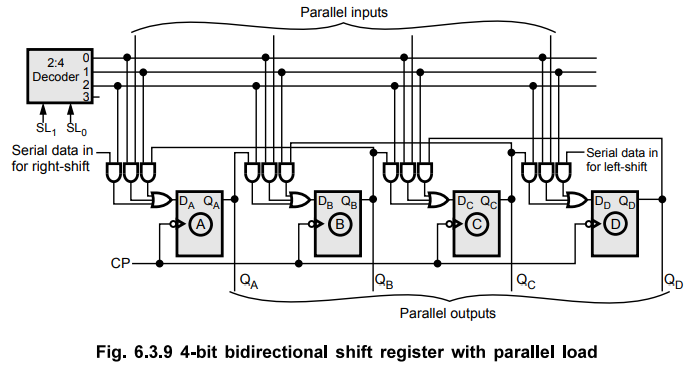

Fig. 6.3.9 shows bidirectional shift register with parallel load.

•

As shown in the Fig. 6.3.9, the D input of each flip-flop has three sources:

Output of left adjacent flip-flop, output of right adjacent flip-flop and

parallel input. Out of these three sources one source is selected at a time and

it is done with the help of decoder. The decoder select lines (SL1

and SL0) select the one source out of three as shown in the Table

6.3.4.

•

When select lines are 00 (i.e. SL1 = 0 and SL0 = 0), data

from the parallel inputs is loaded into the 4-bit register.

•

When select lines are 01 (i.e. SL1 = 0 and SL0 = 1), data

within the register is shifted 1-bit left.

•

When select lines are 10 (i.e. SL1 = 1 and SL0 = 0), data

within the register is shifted 1-bit right.

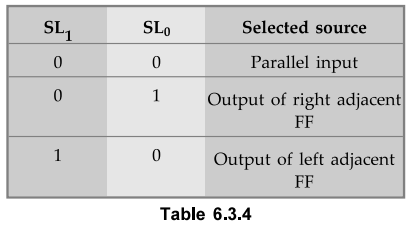

6. Shift Register using JK Flip-flops

•

In section 4.9.5 we have seen that how to construct D flip-flop using JK

flip-flop. By applying complement inputs to J and K we can construct serial-in

serial-out shift right register using JK flip-flops as shown in the Fig.

6.3.10.

Review Questions

1. Draw a 4-bit

serial-in-serial-out shift register and draw its waveforms.

AU CSE May-06,

Dec.-06, Marks 8

2. Draw a 4-bit

parallel-in-serial-out shift register and briefly explain.

AU CSE: May-06, Marks

8

3. Draw the 8-bit

serial-in-parallel-out shift register and explain its operation.

AU CSE Dec.-06, Marks

8

4. Draw and explain

the operation of parallel-in-parallel-out shift register.

AU May-15, Marks 8

5. Explain the

operation of 3-bit bidirectional shift register with the help of neat diagram.

6. Write short notes on SIPO and draw the output waveforms.

AU Dec.-16, Marks 6

Digital Logic Circuits: Unit III: (c) Shift Registers : Tag: : - Types of Shift Registers

Related Topics

Related Subjects

Digital Logic Circuits

EE3302 3rd Semester EEE Dept | 2021 Regulation | 3rd Semester EEE Dept 2021 Regulation