Microprocessors and Microcontrollers: Unit I: (c) 8085 Timing Diagrams

Signal Timings

Questions : 1. In which T-cycle the ALE signal is activated ? 2. Explain how the multiplexed data/address bus is shared for data and address.

Signal Timings

In

8085 microprocessor, signals are activated at specific instant for specific

time period. Once we understand this, it is very easy to draw timing diagrams.

The following section explains when the signals are activated and for what

period they remain in active state.

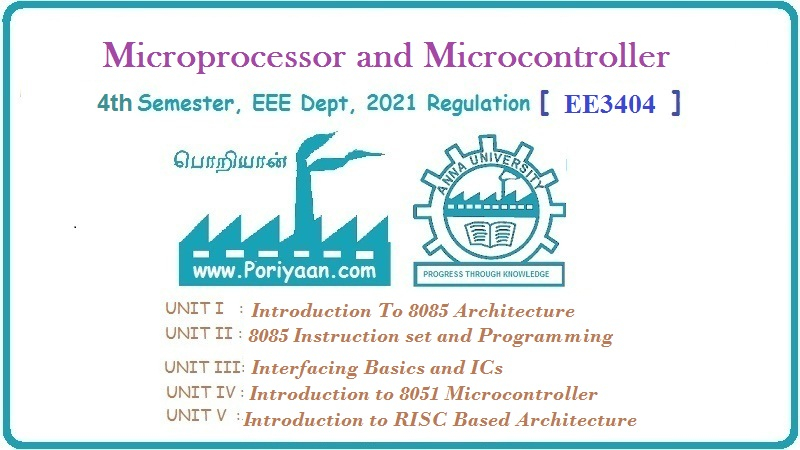

ALE

(Address Latch Enable) :

This

signal is active high signal. It is activated in the beginning of the Testate

of each machine cycle, except bus idle machine cycle and it remains active in

the T1-state as shown in the Fig. 5.3.1.

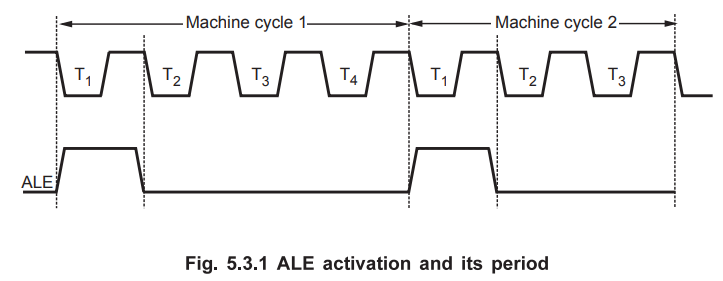

A0

- A7 (Lower byte address) :

The

lower byte of address is available on the multiplexed address/data bus (AD0-AD7)

during T1-state of each machine cycle, except bus idle machine

cycle, as shown in Fig. 5.3.2.

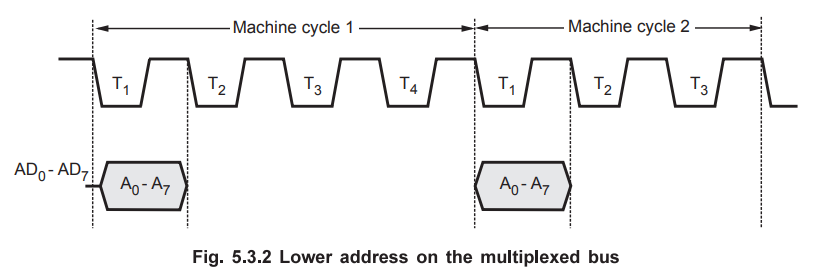

D0

- D7 (Data bus) :

The

data from memory or I/O device and from microprocessor to memory or I/O device

is transferred during T2 and T3 - states. It is important

to note that in read machine cycle, data will appear on the data bus during the

later part of the T2 - state, as shown in the Fig. 5.3.3, whereas in

write cycle data will appear on the data bus at the beginning of the T2

- state, as shown in the Fig. 5.3.3.

To

read data from memory or I/O device it is necessary to select memory or I/O

device. After selection, device will put the data from selected location on the

data bus. This action needs finite time. This time is referred to as 'access

time'. In case of write cycle, data is available in the register set of the

microprocessor and it can put that data on the data bus with zero access time.

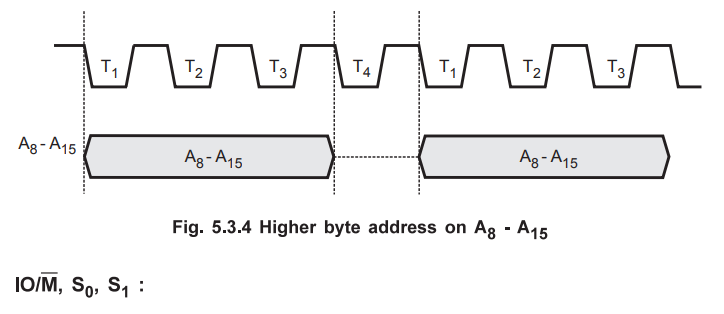

A8

- A15 (Higher byte address) :

The

higher byte of address is available on the A8-A15 bus during Tlz T2 and T3 -

state of each machine cycle, except bus idle machine cycle, as shown in Fig.

5.3.4.

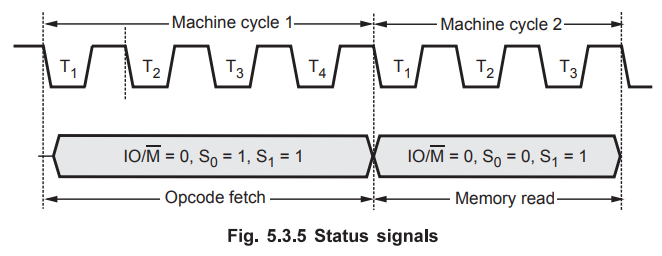

These

signals are called status signals. They decide the type of machine cycle to be

executed. They are activated at the beginning of T1 - state of each

machine cycle and remain active till the end of the machine cycle.

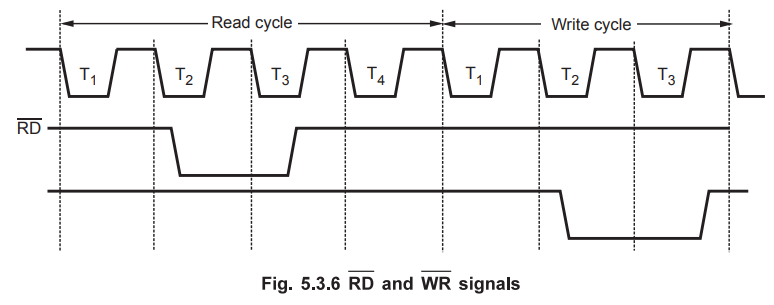

These signals decide the direction of the

data transfer. When

These signals decide the direction of the

data transfer. When ![]() signal is active, data is transmitted from memory

or I/O device to the microprocessor and when

signal is active, data is transmitted from memory

or I/O device to the microprocessor and when ![]() signal is active,

data is transmitted from microprocessor to the memory or I/O device. Both

signals are never active at a time.

signal is active,

data is transmitted from microprocessor to the memory or I/O device. Both

signals are never active at a time.

As we know data transfer in 8085 takes place during T2 and T3, these signals are activated during T2 and T3, as shown in the Fig. 5.3.6.

Review Questions

1. In which T-cycle

the ALE signal is activated?

2. Explain how the multiplexed data/address bus is shared for data and address.

Microprocessors and Microcontrollers: Unit I: (c) 8085 Timing Diagrams : Tag: : - Signal Timings

Related Topics

Related Subjects

Microprocessor and Microcontroller

EE3404 MCU 4th Semester EEE Dept | 2021 Regulation | 4th Semester EEE Dept 2021 Regulation