Digital Logic Circuits: Unit III: (b) Analysis & Design of Synchronous Sequential Circuits

Two Marks Questions with Answers

Analysis & Design of Synchronous Sequential Circuits | Digital Logic Circuits

Digital Logic Circuits: Unit III: (b) Analysis & Design of Synchronous Sequential Circuits : Two Marks Questions with Answers

Two Marks Questions with Answers

Q.1

Give the comparison between synchronous and asynchronous sequential circuits.

(Refer

section 5.1.)

Q.2

Define a state.

AU

: Dec.-06; May-09

Ans.

:

The information stored in the memory elements at any given time defines the

state at that time of the corresponding sequential circuit.

Q.3

What are the classification of sequential circuits ?

Ans.

:

The sequential circuits are classified on the basis of timing of their signals

into two types. They are,

1.

Synchronous sequential circuit.

2.

Asynchronous sequential circuit.

Q.4

What do you mean by present state ?

Ans.

:

The information stored in the memory elements at any given time defines the

present state of the sequential circuit.

Q.5

What do you mean by next state ?

Ans.

:

The present state and the external inputs determine the outputs and the next

state of the sequential circuit.

Q.6

Draw and explain the block diagram of Moore model.

(Refer

section 5.2.1.)

Q.7

What is a Mealy machine ? Give an example.

(Refer

section 5.2.2.)

Q.8

Compare Moore and Mealy models.

(Refer

section 5.2.3.)

Q.9

Define state table.

Ans.

:

For the design of sequential counters we have to relate present states and next

states. The table which represents the relationship between present states and

next states is called state table.

Q.10

What are state diagrams and state tables ?

Ans.

State diagram is a pictorial representation of a behaviour of a sequential

circuit. The state is represented by the circle, and the transition between

states for different input conditions are indicated by directed lines

connecting the circles.

State

table is the translation of state diagram into a tabular form; representing

relationships among input, output and flip-flop states.

Q.11

What is the minimum number of flip-flops needed to design a counter of modulus

60 ?

Ans.

2n ≥ 60 n = 6

Q.12

What is the minimum number of flip-flops required to implement a modulo 21

synchronous counter ?

Ans.

: 2n ≥ 21 n = 5

Thus,

5 flip-flops are required to implement a modulo 21 synchronous counter.

Q.13

How many flip-flops are required to design mod 25 counter ?

Ans.

: 2n

≥ 25 n

= 5

Thus,

5 flip-flops are required to design mod 25 counter.

Q.14

Explain about state reduction or why is state reduction necessary ?

AU

: Dec.-04, 06; May-09

Ans.

:

The state reduction is a technique that reduces the number of states in the

sequential circuit by keeping only one state for two or more redundant/

equivalent states. This reduces the number of required flip-flops and logic

gates, reducing the cost of the final circuit. Two states are said to be redundant

or equivalent, if every possible set of inputs generate exactly same output and

same next state.

Q.15

What is lockout ? How it is avoided ?

AU

: May-12, Dec.-14

Ans.

:

In a counter, if the next state of some unused state is again some unused state,

it may happen that the counter remains in unused states never to arrive at a

used state. Such a condition is called a lockout condition.

To

avoid lockout, the counter should be provided with an additional logic

circuitry which will force the counter from an unused state to the next state

as initial state.

Q.16

What is a self starting counter ?

AU

: May-10

Ans.

:

In a counter if the next state of some unused state is again an unused state

and if by chance the counter happens to find itself in the unused states and

never arrived at a used state then the counter is said to be in the lockout

conditions. The counter which never goes in lockout condition is called self

starting counter.

Q.17

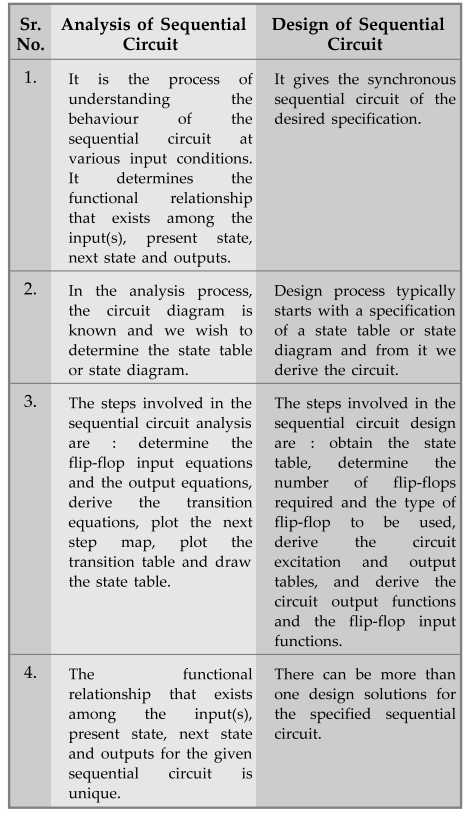

Differentiate between analysis and design of sequential logic circuits.

AU : May-15

Ans.

:

Q.18

State the rules for state assignment.

(Refer

section 5.4.2)

Q.19

State any two differences between Moore and Mealy state machines.

(Refer

section 5.2.3) |

Q.20

Differentiate Mealy and Moore model.

(Refer

section 5.2.3) I

Q.21

What is a presettable counter and ripple counter ?

AU

: Dec.-17

Ans.

:

Presettable counter : Presettable counters are the counters which can be

configured to begin from any value.

Ripple counter : A ripple counter is an asynchronous counter where only the first flip-flop is clocked by an external clock. All subsequent flip-flops are clocked by the output of the preceding flip-flop. Asynchronous counters are also called ripple-counters because of the way the clock pulse ripples it way through the flip-flops.

Digital Logic Circuits: Unit III: (b) Analysis & Design of Synchronous Sequential Circuits : Tag: : Analysis & Design of Synchronous Sequential Circuits | Digital Logic Circuits - Two Marks Questions with Answers

Related Topics

Related Subjects

Digital Logic Circuits

EE3302 3rd Semester EEE Dept | 2021 Regulation | 3rd Semester EEE Dept 2021 Regulation