Digital Logic Circuits: Unit IV: (a) Asynchronous Sequential Circuits

University Questions with Answers (Long Answered Questions)

Asynchronous Sequential Circuits | Digital Logic Circuits

Digital Logic Circuits: Unit IV: (a) Asynchronous Sequential Circuits : University Questions with Answers (Long Answered Questions)

University Questions with Answers

(Long Answered Questions)

(Regulation

2008)

Dec.-10

Q.1

List and explain the steps used for analyzing an asynchronous sequential

circuit. [Section 7.5] [8]

Q.2

When do you get the critical and non-critical races ? How will you obtain race

free conditions ? [Section 7.6] [10]

May-11

Q.3

Describe the steps involved in design of asynchronous sequential circuit in

detail with an example. [Section 7.6] [16]

Dec.-

11

Q.4

State the condition of stability in asynchronous sequential logic. [Section

7.5] [4]

Q.5

When does oscillation occur in an asynchronous sequential logic circuit ?

[Section 7.5] [4]

May-12

Q.6

List and explain the steps used for analyzing an asynchronous sequential

circuit. [Section 7.5] [8]

Dec.-12

Q.7

Describe the steps involved in design of asynchronous sequential circuit in

detail with an example. [Section 7.6] [16]

May-13

Q.8

List and explain the steps used for analyzing an asynchronous sequential

circuit. [Section 7.5] [8]

(Regulation

2013)

Dec.-14

Q.9

Describe with reasons, the effect of races in asynchronous sequential circuit design.

Explain its types with illustrations. Show the method of race-free state

assignments with examples. [Section 7.6] [16]

May-16

Q.10

Explain cycles and races in asynchronous sequential circuits. [Section 7.6.2] [8]

Q.11

What are transition table and flow table ? Give suitable examples. [Section

7.6] [8]

May-17

Q.12

A control mechanism for a vending machine accepts nickels and dimes. It

despense merchandise when 20 cents is deposited; it does not give change if 25

cents is deposited. Design the FSM that implements the required control, using

as few states as possible. Find a suitable assignment and derive next - state

and output expressions. [13]

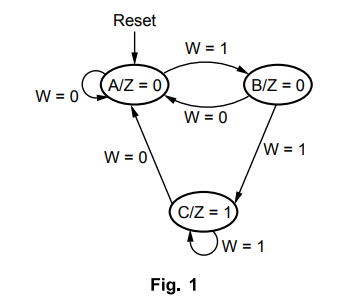

Q.13

Write the VHDL code for the given state diagram, using behavioral modeling.

Design it using one - hot state assignment and implement it using Programmable

Array Logic (PAL). [15]

Dec.-17

Q.14

Design an asynchronous sequential circuit with two inputs x1 and x2 and one

output Z. Initially, both inputs are equal to zero. When x^ or x2 becomes 1,

the output Z becomes 1. When the second input also becomes 1, the output

changes to 0. The output stays at 0 until the circuit goes back to the initial

state. [15]

Q.15

Discuss about the hazards in asynchronous sequential circuit and the ways to

eliminate them. [Section 7.6.3] [13]

Digital Logic Circuits: Unit IV: (a) Asynchronous Sequential Circuits : Tag: : Asynchronous Sequential Circuits | Digital Logic Circuits - University Questions with Answers (Long Answered Questions)

Related Topics

Related Subjects

Digital Logic Circuits

EE3302 3rd Semester EEE Dept | 2021 Regulation | 3rd Semester EEE Dept 2021 Regulation