Digital Logic Circuits: Unit V: VHDL

VHDL Data Types and Operators

• VHDL supports a variety of data types. The type of a variable, signal, or constant determines the operators that are predefined for that object as well as the range of values that it can take on. The VHDL data types can be broadly classified into following five data types :

VHDL Data Types and Operators

AU

: Dec.-11, 12, 15, 16, May-16

•

VHDL supports a variety of data types. The type of a variable, signal, or

constant determines the operators that are predefined for that object as well

as the range of values that it can take on. The VHDL data types can be broadly

classified into following five data types :

1.

Scalar types : The scalar types include numeric data

types and enumerated data types. The numeric types consist of integer, floating

point (real) and physical types. Bit, Boolean and character are all enumerated

types.

2.

Composite types : Array and record types are composite

data types. The values of these types are collection of their elements.

3.

Access types : They are pointers; they provide access

to objects of a given data type.

4.

File type : They provide access to object that

contain a sequence of values of a given type.

5.

Other types : They include the data types provided by

the several external libraries.

1. Scalar Types

•

We have seen that, the scalar types consist of enumeration types, integer

types, physical types, and floating point types. Enumeration, data types and

integer types are called discrete types. On the other hand, integer types,

floating point types and physical types are called numeric types.

Integer

type

•

As the name indicates, it covers all integer values, the values can be positive

or negative. The default range of Integer is -2147483647 to +2147483647.

However, user can specify a shorter range by using the predefined word range.

The shorter range may require less bits to represent the number when binary

encoded. We can define the subtype of base type whose range must be wholly

contained within the bounds of the range of base type.

Examples

:

type

num is integer;

type

long is range -32768 to 32768; -- 16-bit binary encoding.

type

short is range 0 to 255; -- 8-bit binary encoding.

subtype

shorter is short range 0 to 31; -- 5-bit binary encoding.

subtype

shortest is short range 0 to 15; -- 4-bit binary encoding.

Note

:

The encoding of integers in a binary format means that all ranges are rounded

up to the nearest power of two. This means that if shorter had been declared as

:

subtype

shorter is short range 0 to 15;

•

Then the object is synthesized into 4 wires. Objects declared type of type

integer without a range constraint will be synthesized into 32 wires.

Real

(floating point) type

Example

of integer object declaration :

Port

(Il : in integer ;

O1

: out integer);

•

Floating point type definition defines both a type and subtype of that types.

The default range of floating point is -1E38 to + IE38. Like integer type, here

also we can specify the shorter range by using the predefined word range.

Examples

:

type

Real_data is real;

type

Voltage is range to -12.0 to +12.0;

subtype

min voltage is range -5.0 to +5.0;

Example

of real object declaration :

Port

(Il : in real ;

O1

: out real);

Enumerated

types

Bit,

Boolean, Character and severity_level are the enumerated types. These are

defined in a library such as std or ieee.

Bit

data type allows only two values 0 or 1. It is used to describe a signal that

takes only l(High) or 0(Low). The type Boolean has two values, True(l) or

False(0). Both True and False are predefined words.

The

type character constitutes the 128 characters of the ASCII character set. These

character values are called character literals and are always written between

two single quotes (' ')• F°r

example, 'A', ‘_’ ' 3 ' and so on.

An

object with type severity can take one of four values ; note, warning, error or

failure. This type is typically used in assertion statements.

Examples

:

type

Bit is (’0’, 1’);

type

Switch_level is (’0’, ‘1’, ‘x’);

Examples

of enumerated type object declaration :

Port

(Il : in bit;

O1

: out Boolean);

Physical

type

•

Values of a physical type represent measurements of some quantity. Any value of

a physical type is an integral multiple of the base unit of measurement for

that type. For example, time (e.g. second, millisecond, microsecond, etc.) and

voltage (e.g., volt, millivolt, microvolt, etc.)

•

A physical type definition defines both a type and a subtype of that type. Each

unit declaration (either the base unit declaration or a secondary unit

declaration) defines a unit name. Unit name declared in secondary unit

declaration must be directly or indirectly defined in terms of integral

multiples of the base unit of the type declaration in which they appear.

Examples

:

type

time is range -1E18 to 1E18

units

fs;

- femtosecond

ps

= 1000 fs; - picosecond

ns

= 1000 ps; - nanosecond

us

= 1000 ns; - microsecond

ms

= 1000 us; - millisecond

sec

= 1000 ms; - second

min

= 60 sec; - minute

end

units;

type

distance is range 0 to IE 16

units

-

base unit:

A;

- angstrom

-

metric lengths;

nm

= 10 A; - nanometer

um = 1000 nm; -

micrometer (or micron)

mm

= 1000 um; - millimeter

cm

= 10 mm; - centimeter

m

= 1000 mm; - meter

km

= 1000 m; - kilometer

-

- English lengths :

mil

= 254000 A; - mil

inch

= 1000 mil; - inch

ft

= 12 inch; - foot

yd

= 3 ft; - yard

fm

= 6 ft; - fathom

mi

= 5280 ft;- mile

lg

= 3 mi; - league

end

units;

x

: distance; y : time; z : integer;

x

:= 5A + 13 ft - 27 inch; - arithmetic operations

y

: = 3ns + 5 min; - on physical data type

z

: = ns/ps;

x

: = z mi;

y

: = y/10;

•

The arithmetic operations are predefined for all physical types. It is an error

if the execution of such an operation cannot deliver the correct result (that

is, if the value corresponding to the mathematical result is not a value of the

physical type).

User-defined

types

The

user can define a type by using the predefined word type.

Example

:

type

Multi_level_logic is (low, high, rising, falling);

type

arith_op is (add, sub, mul, div);

Here,

multi_level_logic and arith_op are the user defined types. The variables

declared using such data types can take values mentioned in the data type

definition. For example,

Variable

operation : arithop := sub;

Variable

level : Multi_level_logic := high;

2. Composite Types

•

Composite types are used to define collection of values. These include both

arrays of values (collection of values of a single type) and records of values

(collection of values of the same or different types).

• An object of a composite type represents a collection of objects, one for each element of the composite object. A composite type may only contain elements that are of scalar, composite, or access types; elements of file types are not allowed in a composite type. Thus, an object of a composite type ultimately represents a collection of objects of scalar or access types, one for each non-composite subelement of the composite object.

Array

types

•

An array object is a composite object consisting of elements that have the same

subtype. The name for an element of an array uses one or more index values

belonging to specified discrete types. The value of an array object is a

composite value consisting of the values of its elements.

•

An array object is characterized by the number of indices (the dimensionality

of the array), the type, position and range of each index and the type and

possible constraints of the elements. The order of the indices is significant.

•

A one-dimensional array has a distinct element for each possible index value. A

multidimensional array has a distinct element for each possible sequence of

index values that can be formed by selecting one value for each index (in the

given order). The possible values for a given index are all the values that

belong to the corresponding range; this range of values is called the index range.

Example

:

type

num is integer ;

type

numarr is array (7 downto 0) of num;

--

numarr is an array of 8 integer numbers

type

my_word is array (0 to 31) of BIT;

--

a memory word type with an ascending

range

type

datain is array (7 downto 0) of five_level_logic;

--

an input port type with a descending

range

--

Example of unconstrained array

declarations

type

memory is array (integer range o) of myword;

--

a memory array type

-

Examples of array object declarations

signal

dataline : datain ;

--

defines a data input line

variable

mymemory : memory (0 to 2**n-1);

--

defines a memory of 2n 32-bit words

string

and bit_vector are the predefined array types, which are defined in package

std.

The

values of the predefined type string are one-dimensional arrays of the

predefined type character, indexed by values of the predefined subtype

positive;

subtype

positive is integer range 1 to integerhigh;

type

string is array (positive range o) of character;

The

values of the predefined type bit_vector are one-dimensional arrays of the

predefined type BIT, indexed by values of the predefined subtype natural :

subtype

natural is integer range 0 to integerhigh;

type

bit_vector is array (natural range <>) of bit;

-

Examples of string and bit-vector object declaration

variable

message : string (1 to 17) := "This is a message";

signal

low_bite : bitvector (0 to 7);

Record

type

•

A record type is a composite type, objects of which consist of named elements.

The value of a record object is a composite value consisting of the values of

its elements. The record type is analogous to the record datatype in pascal and

the struct declaration in C.

•

A record type definition creates a record types; it consists of the element

declarations, in the order in which they appear in the type definition.

Example

:

type

DATE is

record

DAY

: INTEGER range 1 to 31 ;

MONTH : MONTH_NAME;

YEAR

: INTEGER range 0 to 4000;

end

record;

3. Access Types

•

Values belonging to an access type are pointers to a dynamically allocated

object of some other type. These are similar to pointers in pascal or C

languages.

Example

:

type

ptr is access date;

-

ptr is an access type whose values are

-

addresses that point to object of type date.

4. File Type

•

File types are used to define objects representing files in the host system

environment. The value of a file object is the sequence of values contained in

the host system file.

type_file_type_name

is file of type_name;

•

The type mark in a file type definition defines the subtype of the values

contained in the file. The type mark may denote either a constrained or an

unconstrained subtype. The base type of this subtype must not be a file type or

an access type. If the base type is a composite type, it must not contain a

subelement of an access type. If the base type is an array type, it must be a

one-dimensional array type.

Examples

:

file

of string - Defines a file type that can contain

-

an indefinite number of strings

file

of natural - Defines a file type that can contain

-

only non-negative integer values

•

Three operations are provided for objects of a file type. Given the following

file type declaration :

type

FT is file of TM :

•

Where type mark TM denotes a scalar type, a record type, or a constrained array

subtype, the following operations are implicitly declared immediately following

the file type declaration :

procedure

read (F : in FT; value : out TM);

procedure

write (F : out FT; value: in TM);

function

endfile (F: in FT) return boolean;

•

Procedure read retrieves the next value from a file. Procedure write appends a

value to a file. Function endfile returns False if a subsequent read operation

on an input file can retrieve another value from the file; otherwise it returns

true. Function endfile always returns true for an output file.

5. Other Types

•

There are several other types provided by external library, IEEE. This library

contains a std_logic_1164 package which supports more types. Let us discuss

them.

Std_logic

type

•

std_logic is a data type defined by IEEE standard 1164, and defined in the file

ieee.vhd.std_logic is an enumerated type. This logic has nine values as listed

in Table. 10.6.1.

•

The std_logic data type is very important for both simulation and synthesis.

Std_logic includes values that allow us to accurately simulate such circuit

conditions as unknowns and high-impedance stages. For synthesis purposes, the

high-impedance and don't care values provide a convenient and easily

recognizable way to represent three-state enables and don't care logic. For

synthesis, only the values 0, 1, z and have meaning and are supported.

std_logic_vector type

The

type stdjogic_vector represents an array of bits whose type is stdjogic.

Example

:

Port

(I : in stdjogic_vector (7 downto 0);

O

: out bit);

In

the above example, port I is declared as type std_logic_vector which has

8-bits.

Signed

The

type signed is a numeric type. It is declared in the external package

numeric_std and represents signed integer data in the form of an array. The

left most bit of objects of signed type represents sign and such objects are

represented in 2's complement form, let us see the object definition.

variable

difference : signed (4 downto 0) := 10011;

In

the above definition, the variable difference is declared as signed type and

has 5-bits with initial value 10011, or - 13.

Unsigned

The

type unsigned represents integer data in the form of an array of stdjogic and

it is declared in the external package numeric_std. Let us see the object

definition variable num: unsigned (4 downto 0) := 10011; In the above

definition, the variable num is declared as unsigned type and has 5-bits with

initial value 10011, or 19.

6. Operation in VHDL

VHDL

includes the following kinds of operators :

•

Logical

•

Relational

•

Arithmetic

•

Shift and Rotate

a.

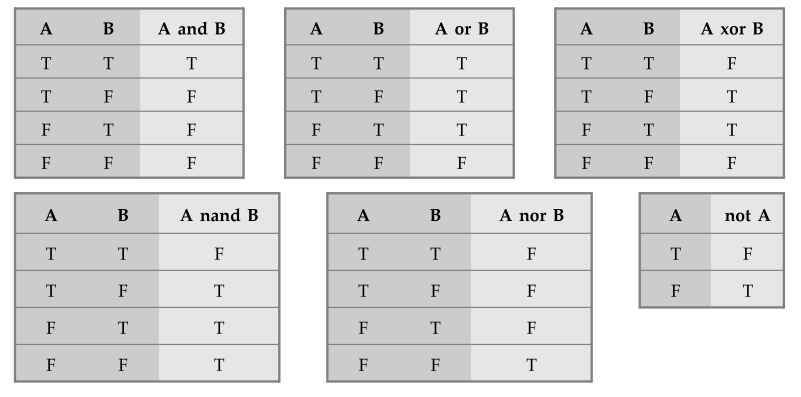

Logical Operators

Logical

operators, when combined with signals and/or variables, are used to create

combinational logic. VHDL provides the logical operators as shown in the Table

10.6.2.

•

These operators are defined for the types bit, std_logic and Boolean, and for

one-dimensional arrays of these types (for example, an array of type bit_vector

or std_logic_vector).

•

The effects of the logical operators are defined in the following tables. The

symbol T represents TRUE for type BOOLEAN, T for type BIT; the symbol F

represents FALSE for type BOOLEAN, 'O' for type BIT.

b.

Relational Operators

•

Relational operators are used to create equality or magnitude comparison

functions. VHDL provides the relational operators as shown in the Table 10.6.3.

•

The following statement demonstrates the use of some of the above relational

operators :

if

(A/=B) then ...

A

is compared to B. If A is equal to B, then the value of the expression (A/= B)

is false (0); otherwise it is true (1).

if

(A > B) then ...

If

A is greater than B, the value of the expression

(A

> B) is true (1); otherwise it is false (0).

Note

:

The operands of each relational operator must be of the same type. The result

type of each relational operator is the predefined type Boolean.

c.

Arithmetic Operators

•

Arithmetic operators are used to create arithmetic functions. Arithmetic

operators provided by VHDL are listed in Table 10.6.4.

d.

Shift and Rotate Operators

•

These operators shift or rotate the bits of the operand right or left by some

specified number of bit positions. There are two types of shift operators :

Logic shift operator and arithmetic shift operator. When logical shift operator

is used, the vacant positions created due to shift operation are filled with

zeros. On the other hand, when arithmetic right shift operator is used the

vacant positions created due to shift operation are filled with MSB (sign bit).

The arithmetic left shift is same as the logical left shift.

•

The Table 10.6.5 shows the shift and rotate operators supported in VHDL. To

understand the function of these operators, assume that operand A is the 4-bit

vector with value 1101.

Note

:

•

Shift left by 1 bit performs multiplication by two while shift right by 1 bit

performs division by two.

•

With rotate operation we can restore the original contents after one complete

cyclic rotation. This is not the case with shift operation.

e.

Operators Precedence

•

The precedence of operators is shown in Table 10.6.6. The operators belongs to

same row have the same precedence level. Operators are listed in order of

decreasing precedence.

•

Operators of higher precedence are associated with their operands before operators

of lower precedence. For a sequence of operators with the same precedence

level, the operators are associated with their operands in textual order, from

left to right. The precedence of an operator is fixed and may not be changed by

the user, but parentheses can be used to control the association of operators

and operands.

Review Questions

1. List and briefly explain different data types supported by

VHDL.

2. What are the operators present in VHDL ?

AU : Dec.-11, 12, 15, Marks 2

3. Explain the various operators supported by VHDL.

4. Write short notes on built-in operators used in VHDL

programming.

Digital Logic Circuits: Unit V: VHDL : Tag: : - VHDL Data Types and Operators

Related Topics

Related Subjects

Digital Logic Circuits

EE3302 3rd Semester EEE Dept | 2021 Regulation | 3rd Semester EEE Dept 2021 Regulation