Digital Logic Circuits: Unit III: (a) Flip-Flops

Asynchronous or Direct Inputs

Flip-Flops

• For the flip-flops discussed so far, the SR, D, JK, and T, the inputs are called synchronous inputs because data on these inputs are transferred to the flip-flop's output only on the triggering edge of the clock pulse; that is, the data are transferred synchronously with the clock.

Asynchronous or Direct Inputs

•

For the flip-flops discussed so far, the SR, D, JK, and T, the inputs are

called synchronous inputs because data on these inputs are transferred to the

flip-flop's output only on the triggering edge of the clock pulse; that is, the

data are transferred synchronously with the clock.

•

When power is turn ON, the state of the flip-flop is uncertain. It may come to

set (Q = 1) or reset (Q = 0) state. In many applications, it is necessary to

initially set or reset the flip-flop.

Such

initial state of flip-flop can be accomplished by using the direct or

asynchronous inputs of the flip-flop. These inputs are :  They

can be applied at any time between clock pulses and are not in synchronism with

the clock.

They

can be applied at any time between clock pulses and are not in synchronism with

the clock.

•

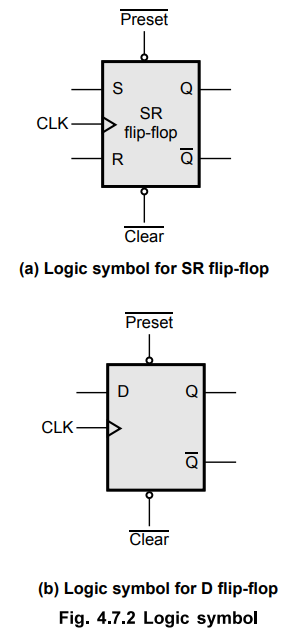

The Fig. 4.7.1 shows the SR and D flip-flops with preset and clear inputs.

These are active-low inputs and thus when  the circuit operates in

accordance with the truth table of SR flip-flop. If

the circuit operates in

accordance with the truth table of SR flip-flop. If  , the

flip-flop is reset and

, the

flip-flop is reset and  the flip-flop is set.

the flip-flop is set.

Note

: Condition

P = C = 0 must not be used, since this leads to an uncertain state.

Digital Logic Circuits: Unit III: (a) Flip-Flops : Tag: : Flip-Flops - Asynchronous or Direct Inputs

Related Topics

Related Subjects

Digital Logic Circuits

EE3302 3rd Semester EEE Dept | 2021 Regulation | 3rd Semester EEE Dept 2021 Regulation