Digital Logic Circuits: Unit III: (a) Flip-Flops

Two Marks Questions with Answers

Flip-Flops | Digital Logic Circuits

Digital Logic Circuits: Unit III: (a) Flip-Flops : Two Marks Questions with Answers

Two Marks Questions with Answers

Q.1

Define a sequential logic circuit. Give an example.

AU

: May-08

Ans.

:

The circuits in which the output variables depend not only on the present input

but they also depend upon the past history of these input variables are known

as sequential logic circuits. Flip-flops, counters, registers are the examples

of sequential logic circuit.

Q.2

What are synchronous sequential circuits ?

AU

: May-10, 14

Ans.

:

Synchronous sequential circuits are those in which signals can affect the

memory elements only at discrete instants of time. Clocked flip-flops are

examples of synchronous sequential circuits.

Q.3

Differentiate between combinational and sequential circuits. (Refer section

4.1.1)

Q.4

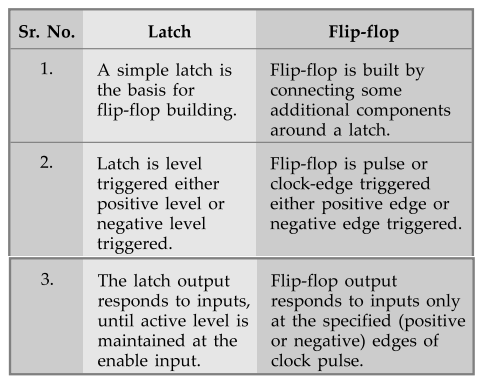

Differentiate between flip-flop and latch.

Ans

. :

Q.5

Give the meaning for edge triggering in flip-flops.

Ans.

:

In the edge triggering, the output responds to the changes in the input only at

the positive or negative edge of the clock pulse at the clock input. There are

two types of edge triggering.

•

Positive edge triggering : Here, the output responds to the

changes in the input only at the positive edge of the clock pulse at the clock

input.

•

Negative edge triggering : Here, the output responds to the

changes in the input only at the negative edge of the clock pulse at the clock

input.

Q.6

Draw the circuit of SR flip-flop. AU : May-10

(Refer

section 4.2)

Q.7

Draw the logic circuit of a clocked JK flip-flop.

(Refer

section 4.4)

Q.8

What is the operation of D flip-flop ?

Ans.

:

In D flip-flop during the occurrence of clock pulse if D = l, the output Q is

set and if D = 0, the output is reset.

Q.9

Draw truth table for JK flipflop.

(Refer

Fig. 4.4 (c))

Q.10

What is the operation of JK flip-flop ?

Ans.

:

•

When K input is low and J input is high the Q output of flip-flop is set.

•

When K input is high and J input is low the Q output of flip-flop is reset.

•

When both the inputs K and J are low the output does not change

•

When both the inputs K and J are high the output toggle on the next positive

clock edge.

Q.11

What is the operation of T flip-flop ?

Ans.

:

T flip-flop is also known as Toggle flip-flop.

•

When T = 0 there is no change in the output.

•

When T = 1 the output switch to the complement state (i.e.) the output toggles.

Q.12

With reference to a JK flip-flop, what is racing ?

AU

: May-04, Dec.-08, 11, 17

Ans.

:

In a level triggered J-K flip-flop, when J and K are both high, then the output

toggles continuously. This condition is called a race around condition.

Q.13

What is a master-slave flip-flop ?

Ans.

:

A master-slave flip-flop consists of two flip-flops where one circuit serves as

a master and the other as a slave. The output of the master flip-flop is fed as

an input to the slave flip-flop. The master flip-flop is triggered at the

positive edge of the clock and slave flip-flop is triggered at the negative

edge of the clock.

Q.14

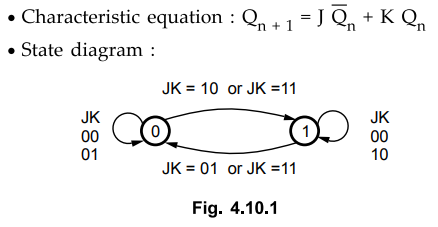

Give the characteristic equation and state diagram of JK flip-flop.

Ans.

:

Q.

15 If the input frequency of a T FF is 1600 kHz, what will be the output

frequency ? Give reason for your answer.

Ans.

:

800 kHz, because it toggles at every clock pulse.

Q.

16 Give the excitation table of SR flip-flop.

(Refer

section 4.8.3.1)

AU

: Dec.-03

Q.

17 Give the excitation table for JK flip-flop.

(Refer

section 4.8.3.2) I

AU

: May-05, 06, June-09

Q.

18 Obtain the excitation table of D and JK flip-flops.

(Refer

sections 4.8.3.3 and 4.8.3.2) I

Q.

19 Give the state diagram of JK FF.

(Refer

section 4.8.2)

AU

: May-07, 10, Dec.-12

Q.

20 Convert JK FF to D FF. (Refer section 4.9.5)

Q.21

The JK flip-flop is an universal flip-flop. Justify.

AU

: Dec.-12

Ans.

:

The JK flip-flop is called an universal flip-flop because it can be easily

configured to work as any other flip-flops such as T flip-flop, D flip-flop and

SR flip-flop.

Q.22

Define registers.

Ans.

:

A register is a group of flip-flops. So an n-bit register has a group of n

flip-flops and is capable of storing any binary information/number containing

n-bits.

Q.23

Define shift registers.

Ans.

:

The binary information in a register can be moved from stage to stage within

the register or into or out of the register upon application of clock pulses.

This type of bit movement or shifting is essential for certain arithmetic and

logic operations used in microprocessors. Ibis gives rise to group of registers

called shift registers.

Q.24

What are the different types of shift type ?

Ans.

:

There are five types. They are,

•

Serial In Serial Out Shift Register

•

Serial In Parallel Out Shift Register

•

Parallel In Serial Out Shift Register

•

Parallel In Parallel Out Shift Register

•

Bidirectional Shift Register

Q.25

What is the difference between serial and parallel transfer ? What type of

register is used in each case ?

AU

: Dec.-07

Ans.

:

When data is transferred one bit at a time, the process of transfer is known as

serial transfer. When multiple bits of data are transferred at a time, the

process is known as parallel transfer. For parallel transfer, we can use

parallel in and parallel out register. For serial transfer we can use left

shift or right shift register.

Q.26

What is the drawback of SR flip-flop

AU

: May-14

Ans.

:

For SR flip-flop, when SR inputs are S = R = 1, output is unpredictable. This

is the drawback of SR flip-flop.

Q.27

Show how the JK flip flop can be modified into a D flip flop or a T flip-flop.

(Refer sections 4.9.5 and 4.9.4) AU

: Dec.-14

Q.28

Mention the major application of master slave flip-flop. (Refer section 4.5) AU

: Dec.-l0

Q.29

Sketch the state diagram of D flip-flop. (Refer section 4.8)

AU

: Dec.-12

Q.30 Draw state diagram of SR flip-flop.

(Refer

section 4.8) AU : Dec.-l0

Q.31

Obtain the excitation table of D flip-flop.

(Refer

section 4.8) AU : May-06

Q.32

Convert JK flip-flop to T flip-flop.

(Refer

section 4.9) AU : Dec.-l0

Q.33

Draw the truth table and state diagram of SR flip-flop.

(Refer

section 4.2 and 4.8.2) AU : Dec.-15

Q.34

What is edge triggered flip-flops ?

(Refer

section 4.1.3) AU : Dec.-15

Q.35

Convert T Flip Flop to D flip-flop.

(Refer

section 4.9.7) AU : May-15

Q.36

Give the characteristic equation and characteristic table of SR flip-flop.

(Refer

Fig. 4.2.2) AU : May-16

Q.37

Draw the state diagram of JK flip flop.

(Refer

section 4.8.2) AU : Dec.-16

Q.38 Give the characteristic equation and characteristic table of a T Flip Flop. (Refer section 4.6) AU : May-17

Digital Logic Circuits: Unit III: (a) Flip-Flops : Tag: : Flip-Flops | Digital Logic Circuits - Two Marks Questions with Answers

Related Topics

Related Subjects

Digital Logic Circuits

EE3302 3rd Semester EEE Dept | 2021 Regulation | 3rd Semester EEE Dept 2021 Regulation